Channel Modeling and Coding for Next-Generation Memories and Storage

- Advanced graph based and algebraic codes for ultra dense non-volatile memories.

- Advanced graph based coding methods for future HDDs.

- Sneak path mitigation in resistive memories.

- Channel modeling and analysis.

- New data representation schemes.

- Asymmetric coding for Flash.

Overview

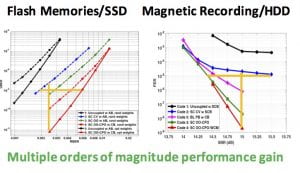

All modern data storage systems and memories require increasingly high levels of reliability. While channel coding methods have been a reliable workhorse since the early days of computer storage, conventional techniques are no longer appropriate in the context of new applications: traditional methods are almost universally designed to optimize for the Hamming metric, yet modern memories and storage exhibit a very high levels of asymmetry and non-uniformity. Using symmetric error correcting codes in such applications is not only mathematically suboptimal but also wasteful of precious system resources.

Recent results

In our work, we deliberately depart from optimizing for the Hamming metric and focus on code designs that are attuned to the physical characteristics of the underlying devices. We explore a variety of innovative code construction techniques, by combining tools from combinatorial graph theory, convex optimization, and abstract algebra. Our rich code repertoire includes many state of the art constructions for an array of different applications.

In our work, we deliberately depart from optimizing for the Hamming metric and focus on code designs that are attuned to the physical characteristics of the underlying devices. We explore a variety of innovative code construction techniques, by combining tools from combinatorial graph theory, convex optimization, and abstract algebra. Our rich code repertoire includes many state of the art constructions for an array of different applications.

Additionally, we offer system level perspectives of our mathematical solutions for a broad spectrum of applications, from on-chip memories to Flash to magnetic recording.

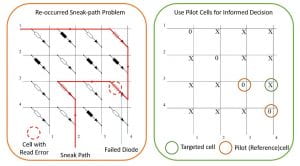

More recently we have investigated resistive random-access memory (ReRAM) with the crossbar structure, as it is one promising candidate to be used as a next generation non-volatile memory device. In a crossbar ReRAM, in which a memristor is positioned on each row-column intersection, the sneak-path problem is one of the main challenges for a reliable readout. The sneak-path problem can be solved with additional selection devices. When some selection devices fail short, the sneak-path problem re-occurs.

More recently we have investigated resistive random-access memory (ReRAM) with the crossbar structure, as it is one promising candidate to be used as a next generation non-volatile memory device. In a crossbar ReRAM, in which a memristor is positioned on each row-column intersection, the sneak-path problem is one of the main challenges for a reliable readout. The sneak-path problem can be solved with additional selection devices. When some selection devices fail short, the sneak-path problem re-occurs.

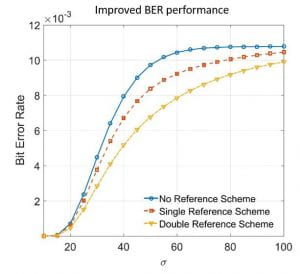

The re-occurred sneak-path event can be described combinatorially and its adverse effect can be modeled as a parallel interference. Based on a simple pilot construction, we probabilistically characterized the inter-cell dependency of the re-occurred sneak-path events. Utilizing this dependency, we proposed adaptive thresholding schemes for resistive memory readout using side information provided by pilot cells. This estimation theoretic approach effectively reduces the bit-error rate while maintaining low redundancy overhead and low complexity.

The re-occurred sneak-path event can be described combinatorially and its adverse effect can be modeled as a parallel interference. Based on a simple pilot construction, we probabilistically characterized the inter-cell dependency of the re-occurred sneak-path events. Utilizing this dependency, we proposed adaptive thresholding schemes for resistive memory readout using side information provided by pilot cells. This estimation theoretic approach effectively reduces the bit-error rate while maintaining low redundancy overhead and low complexity.

Our group has a distinguished record of research contributions in this domain.

Representative recent publications include both review articles and original contributions:

Review articles

- S. S. Garani, L. Dolecek, J. Barry, F. Sala, and B. Vasic, “Signal Processing and Coding Techniques for 2-D Magnetic Recording: An Overview,” Proceedings of the IEEE, vol. 106 (9), pp. 286-318, Feb. 2018.

- L. Dolecek and Y. Cassuto, “Channel Coding for Nonvolatile Memory Technologies: Theoretical Advances and Practical Considerations,” Proceedings of the IEEE, vol. 105 (9), pp. 1705-1724, Sept. 2017.

- L. Dolecek and F. Sala, “Channel Coding Methods for Non-Volatile Memories,” Foundations and Trends in Communications and Information Theory, Vol. 13 (1), pp. 1- 136, February 2016.

- F. Sala, C. Schoeny, and L. Dolecek, “Advanced Algebraic and Graph-Based ECC Schemes for Flash Memories,” to appear in 3-D Flash Memories, Ed. Rino Micheloni, Springer, 2016.

- F. Sala, K. A. S. Immink, and L. Dolecek, “Error Control Schemes for Modern Flash Memories: Solutions for Flash Deficiencies,” IEEE Consumer Electronics, vol. 4 (1), pp. 66-73, Jan. 2015.

- L. Dolecek, M. Blaum, S. Bruck, A. Jiang, K. Ramchandran, and B. Vasic, “Guest Editorial: Communication Methodologies for the Next Generation Data Storage Systems,” IEEE Journal on Selected Areas in Communications, vol. 32 (5), pp. 825- 830, May 2014.

Graph-based codes for Flash and HDDs.

- A. Hareedy, R. Wu, and L. Dolecek, “A Channel-Aware Combinatorial Approach to DesignHigh Performance Spatially-Coupled Codes for Magnetic Recording Systems,” IEEE Transactions on Information Theory, vol. 66 (8), pp. 4834- 4852, Aug. 2020.

- A. Hareedy, C. Lanka, N. Guo, and L. Dolecek, “A Combinatorial Methodology for Optimizing Non-Binary Graph-Based Codes: Theoretical Analysis and Applications in Data Storage,” IEEE Transactions on Information Theory, vol. 65 (4), pp. 2128 – 2154, Apr. 2019. IEEE Data Storage Society 2019 Best Student Paper Award.

- Esfahanizadeh, A. Hareedy, R. Wu, R. Galbraith, and L. Dolecek, “Spatially-coupled codes for channels with SNR variation,” IEEE Transactions on Magnetics, vol. 54, no. 11, Nov. 2018, Art. no. 9401505.

H. Esfahanizadeh, A. Hareedy, and L. Dolecek, “Spatially-Coupled Codes Optimized for Magnetic Recording Applications,” IEEE Transactions on Magnetics, vol. 53 (2), pp. 1 — 11, Feb. 2017. - A. Hareedy, C. Lanka, and L. Dolecek, “A General Non-Binary LDPC Code Optimization Framework Suitable for Dense Flash Memory and Magnetic Storage,” IEEE Journal On Selected Areas of Communications (JSAC) — Special Issue on Data Storage, Sept. 2016.

- A. Hareedy, B. Amiri, S. Zhao, R. Galbraith, and L. Dolecek, “Non-Binary LDPC Code Optimization for Partial Response Channels,” in Proc. IEEE Globecom, Dec. 2015. Best paper award.

Signal Processing for Emerging Memories.

- Z. Chen, C. Schoeny, L. Dolecek, “Pilot Assisted Adaptive Thresholding for Sneak-Path Mitigation in Resistive Memories With Failed Selection Devices,” IEEE Transactions on Communications, vol. 68(1), pp. 66-81, Jan. 2020.

- Z. Chen and L. Dolecek, “Write and Read Channel Models for 1S1R Crossbar Resistive Memory with High Line Resistance,” IEEE GLOBECOM, 2020.

Algebraic Codes and Signal Processing for NVMs.

- R. Gabrys, E. Yaakobi, F. Farnoud, F. Sala, S. Bruck, and L. Dolecek, “Codes Correcting Erasures and Deletions for Rank Modulation“, IEEE Transactions on Information Theory, vol. 62 (1), pp. 136 — 150, January 2016.

- F. Sala, C. Schoeny, D, Divsalar, and L. Dolecek, “Asymmetric ECCs for Flash in High Radiation Environments,” IEEE Asilomar Conference on Signals, Systems and Computers, Monterey, CA, Nov. 2015 (invited).

- C. Schoeny, F. Sala, and L. Dolecek, “Analysis and Coding Schemes for the Flash Normal-Laplace Mixture Channel,”in Proc. IEEE International Symposium on Information Theory (ISIT), Hong Kong, June, 2015.

- R. Gabrys, E. Yaakobi, and L. Dolecek, “Correcting Grain-Errors in Magnetic Media,” IEEE Transactions on Information Theory, vol. 61 (5), pp.2256 — 2272, May 2015.

- R. Gabrys and L. Dolecek, “Constructions of Non-binary WOM Codes for Multilevel Flash Memories,” IEEE Transactions on Information Theory, vol. 61 (4), pp. 1905-1919, April 2015.

- R. Gabrys, F. Sala, and L. Dolecek, “Coding for Unreliable Flash Memory Cells,” IEEE Communication Letters, vol 18 (9), pp. 1491 — 1494, July 2014.

- R. Gabrys, E. Yaakobi and L. Dolecek, “Graded bit error correcting codes with applications to flash memory,” IEEE Transactions on Information Theory, vol. 59(4), pp. 2315 — 2327, Apr. 2013.

- F. Sala, R. Gabrys and L. Dolecek, “Dynamic threshold schemes for multi-level non-volatile memories,” IEEE Transactions on Communications, vol. 61 (7), pp. 2624 – 2634, Jul. 2013.

Coding for on-chip memories.

- F. Sala, H. Duwe, L. Dolecek, and R. Kumar, “A Unified Framework for Error Correction Techniques in On-Chip Memories,” SELSE Workshop and DSN Conference, 2016. Best of Selse Award.